电路原理图作为电子产品设计的核心部分,进行高质量/高效率设计与验证成为保证研发高效迭代、高品质产品的重要前提。原理图检查工具以及部分定制化可解决人为疏忽造成的检视遗漏,节省设计师原理图检查耗费的大量时间和金钱,简化整个设计流程,加快产品上市时间。

传统原理图设计审查缺点:

- 审查过程主要依靠人工检查,费时费力。

- 人工检查,容易遗漏。

- 无法形成快速完整的检查报告。

- 问题需要在图纸中反复查找,设计审查效率极低。

- 工程师自己对自己的“成果”,容易形成惯性思维,无法检查出错误。

- 检察人员检查出问题后,需要人工形成报表,无法在原理图工具中自动定位。

- 不便于知识的持续积累与复用。

- 无法有效的将设计知识规则条目应用到实际设计检验中。

CMS? Schematic Audit电路原理图检查工具是专门应用于对电路设计过程在原理图阶段存在潜在电路逻辑设计问题的在线互动式交叉检查分析。

优势及特点

- 统一审查条目规则管理,支持分类管理。

- 支持设计检查规则的参数化配置。

- 支持服务器规则数据统一管理,支持规则版本管理。

- 自动审查原理图,缩短审查周期,提高研发效率。

- 支持OrCAD Capture/Design EntryHDL等EDA设计软件无缝集成。

- 支持设计审查结果和设计数据绑定,能快速定位到问题在设计中的具体位置,定位问题更快速。

- 支持逻辑电气规则、安规规则、信号完整性、电源完整性、引脚合理性、降额分析、模块接口分析等分析项目。

- 支持与设计ERC/DRC集成分析。

- 快速保存审查结果数据。

- 支持输出模板可定制化。

- 支持设计审查规则可定制化。

- 支持用户及权限管理。

功能模块

- 电气规则知识库管理模块

- 电气设计规则集成自动化分析模块

- 检查输出与统计分析模块

- 用户与权限管理模块

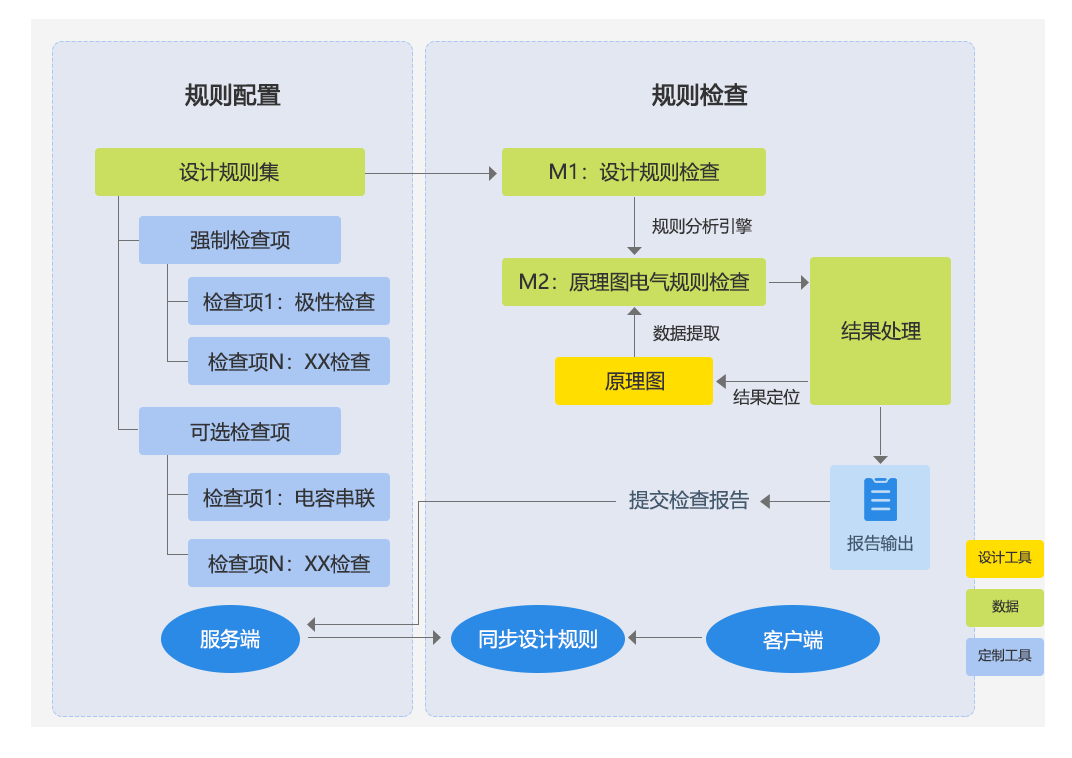

原理图检查工具软件设计业务流程见下图所示。

原理图检查工具软件系统框图

CMS Schematic Audit软件帮助用户构建设计规范管理,实现原理图规则自动化交互式分析。以下为常见的检查条目。

| 条目号 | 规则集项目 |

|---|---|

| 1 | 孤立网络检查 |

| 2 | 器件极性检查 |

| 3 | 悬空管脚检查 |

| 4 | 原理图一次电源电容串联检查 |

| 5 | 原理图拆分器件完整性检查 |

| 6 | 原理图FPGA差分信号配对检查 |

| 7 | 原理图FPGA电源连接检查 |

| 8 | 电容降额设计检查 |

| 9 | 同类阻容感器件检查 |

| 10 | 各种类型的上下拉检查 |

| 11 | 检查元器件连接电源或接地的正确性 |

| 12 | POWER属性引脚未连接检查 |

| 13 | 电源去耦电容数量完整性检查 |

| 14 | 异常的时钟信号无串阻 |

| 15 | 网络命名检查 |

| 16 | 原理图差异检查 |

| 17 | 系统自动命名产生的网络汇总 |

| 18 | BJT器件的基极是否缺少电阻 |

| 19 | 检查总线的位数 |

| 20 | 器件优选检查 |

| 21 | 连接器信号和地管脚数量比值检查 |

这些检查您是否还在手动依靠纸面的规则条目检查?如果是,来试试迪浩打造的这款CMS Schematic Audit。

这款软件完全按照用户习惯,具有自动化的分析流程;同时,提供客户规则条目定制化开发并集成到该软件中集中化管理。软件完全集成EDA设计工具(Cadence/OrCAD/Mentor/Altium),帮助您提高设计效率。软件具有自动载入器件、网表信息,无需人工干预;支持原理图批量和单条检查;支持多原理图对比和结果展示;支持检查结果状态显示,如:正确、警告、错误状态;支持错误快速定位,提高检查效率。