CMS? Schematic Audit

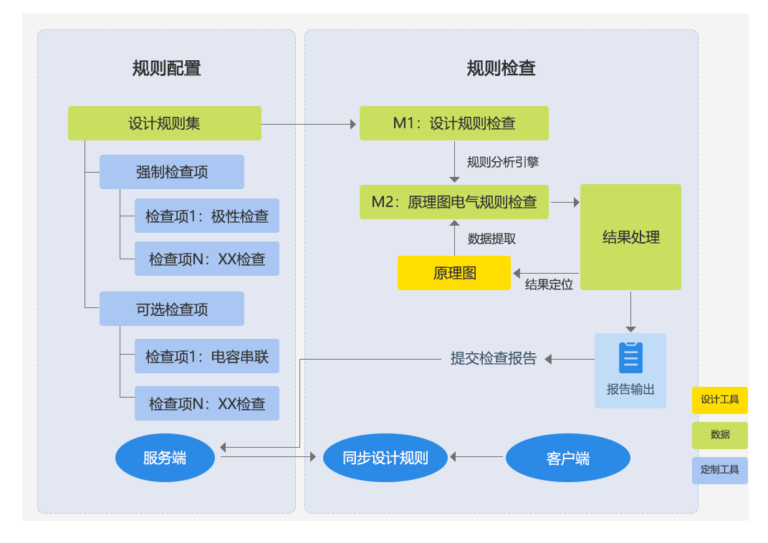

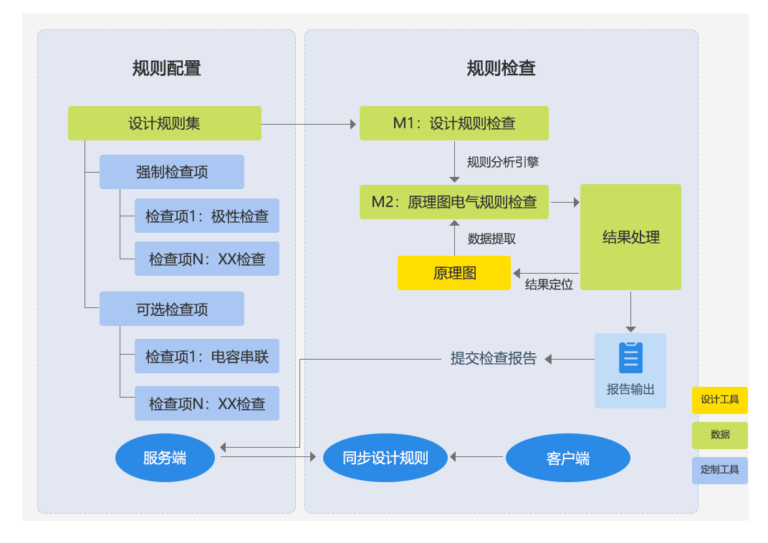

电路原理图作为电子产品设计的核心部分,进行高质量/高效率设计与验证成为保证研发高效迭代、高品质产品的重要前提。原理图检查工具以及部分定制化可解决人为疏忽造成的检视遗漏,节省设计师原理图检查耗费的大量时间和金钱,简化整个设计流程,加快产品上市时间。 传统原理图设计审查缺点: 审查过程主要依靠人工检查,费时费力。 人工检查,容易遗漏。 无法形成快速完整的检查报告。 问题需要在图纸中反复查找,设计审查效

电路原理图作为电子产品设计的核心部分,进行高质量/高效率设计与验证成为保证研发高效迭代、高品质产品的重要前提。原理图检查工具以及部分定制化可解决人为疏忽造成的检视遗漏,节省设计师原理图检查耗费的大量时间和金钱,简化整个设计流程,加快产品上市时间。 传统原理图设计审查缺点: 审查过程主要依靠人工检查,费时费力。 人工检查,容易遗漏。 无法形成快速完整的检查报告。 问题需要在图纸中反复查找,设计审查效

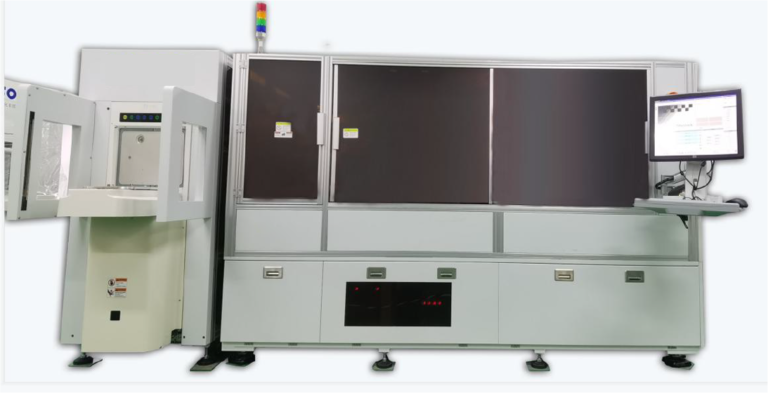

BGA/CSP chip level ball mounting machine MBA-1000 针对 BGA 芯片的批量生产特点,研制专用承载 台治具,一次性可同时放置 120 枚 BGA 芯片, 高性价比. 设备特征 1) 适用于 BGA/CSP 芯片批量植球,单次搭载芯片可达 120 颗; 2) 人工上下料、自动印刷/植球,设备性价比高; 3) 对应锡球直径:0.20mm-1.00mm;4

可对应 3-12 英寸各类材质的晶圆; 可对应 Foup、FOSB、SMIF、Open Cassette; 可对应可 OHT 系统和 AGV 系统相配套; 可对应 MES 系统; 满足用户的各种应用方式(夹持、伯努利、翻转)和 14 纳米工艺需求; 除了通用的 2-8 port 产品外,可根据客户的需求定制各类型排列方式。

WAFER LEVEL MICROBALL MOUNTER WMB-2000 适用于 8/12 寸晶圆,通过高精度丝网印刷和视觉 图像处理技术,微球精准对位搭载,实现 WLCSP 封装工艺。替代了传统晶圆电镀凸点制作方法, 大幅降低成本,实现了一次性搭载,具有安定化 批量生产和高搭载率的优势。 设备特征 独创丝网和台面全自动清洁机构,保证植球良率; 采用了集成有 MES 模块的控制软件,实现信息化

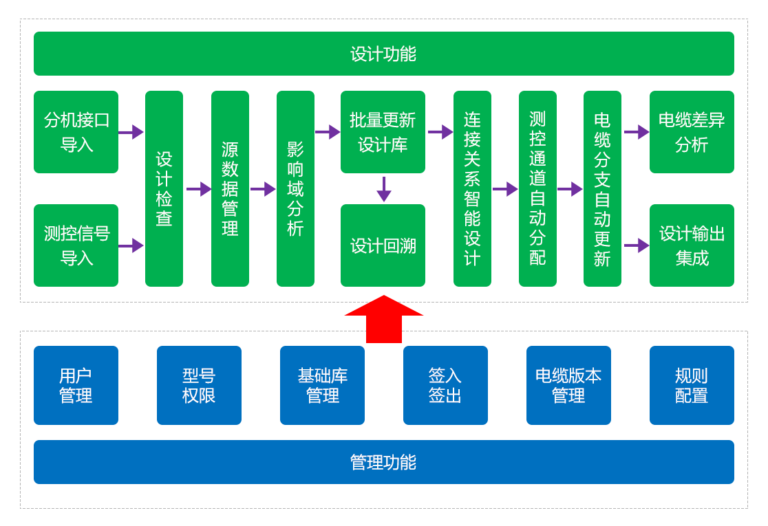

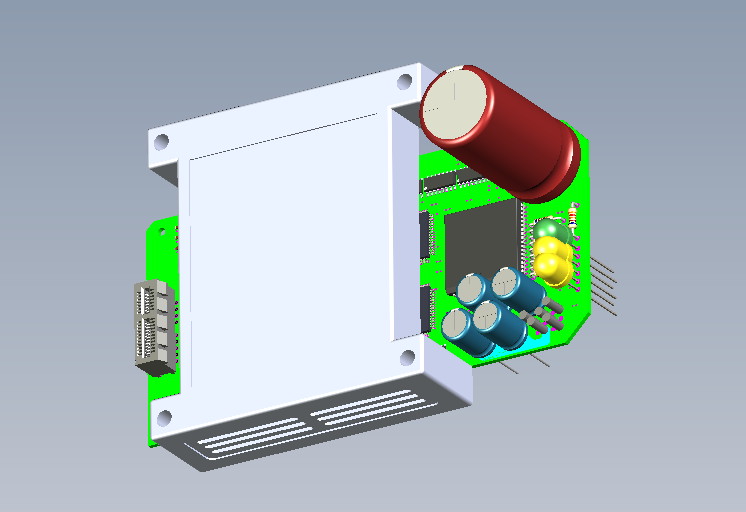

对于复杂电子系统产品的电气设计,从硬件架构层次来看,都是由多个部件或者多个电路板组成的系统。因此,对于电气产品的硬件研发过程,包含: 系统的电气(线缆网)系统设计、单板设计、电气电路仿真分析、系统仿真分析等。

通过高速周期性(high-speed cycle-by-cycle)的仿真来展示真实的大信号性能,采用精确建模技术进行电流模式控制仿真;进行CCM和DCM转换器仿真;分析控制系统的环路增益,输入滤波器的设计和分析;对所有主要器件进行功率损耗测量和电应力分析。总之,通过建模和仿真您可以对整个电源系统进行完整的模拟。 主要特点 分析大信号产生的影响,例如启动瞬态、功率级半导体承载应力和负载阶跃响应。

众所周知,优秀电子系统是通常需要工程师设计严谨、严格按照设计准则和经验来精确把握每一个设计细节,才能确保高质量的作品诞生,传统的设计需要面临信号完整性、电源完整性、EMI电磁特性、工艺制造性及设计标准化和规范化等要求,往往在电路设计完成后由企业内部组织专业或资深技术人员进行会议交叉评审,整理反馈建议,交由设计师修改,再评审迭代,直至无误方能进行下一流程,这会带来评审过程费时费力,且不能及时快速反馈

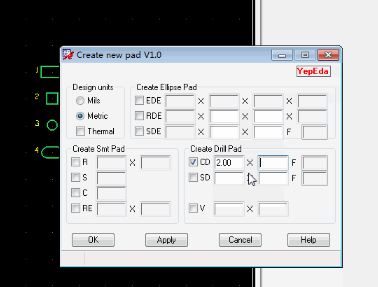

提供与Cadence Allegro PCB集成的设计检查和设计增强功能,覆盖了快速化设计定义、快速设计检查、快速设计建库和快速输出等功能。 该模块基于AXL-Skill脚本语言开发,与Cadence工具菜单无缝集成,实现在PCB设计环境的初始化,快捷布局布线设定,约束环境定义、电气规则检查和DFX工艺规则在线分析检查,输出检查报告。 软件界面: 软件安装完成后,分为Yep Designer、La